Design Services

Apex Semiconductor’s design services provides turnkey solutions from specifications to packaged parts that can be productized. From dedicated ASICs to complex SoCs, we work closely with our customers to effectively achieve all requirements. The Apex Semiconductor team offers decades of experience in developing products and providing design services. Our extensive product experience enables flawless design and first-pass silicon success to our design service customers.

Our design services encompass a wide range of applications spanning high-performance and low-power microprocessors, networking and storage, AI accelerators, and automotive designs. We specialize in turning your ideas and specifications into working silicon. Our team has vast experience in advanced process nodes and has executed on multiple tapeouts with large die sizes. We work in close partnership with our customers and become an extended engineering team, available around the clock with our design centers in the US and India. Through our partnership with leading foundries, we provide customers with access to various process technologies, including the advanced nodes for their respective tapeouts.

Apex’s Value Proposition

We are veterans of the semiconductor industry and have worked in multiple start-ups and large multinational companies. The team boasts an average experience of greater than twenty years and has been working together for more than fifteen years. Our track record consists of successful execution on SoCs such as Intel-class microprocessors, Nvidia-class GPUs, networking and storage chips, and mixed-signal designs. We specialize in all aspects of SoC design starting from RTL to New Product Introduction (NPI). The team has many years of experience with leading EDA vendor tools and can collaborate with EDA vendor R&D teams directly through our partnerships. Furthermore, the team has performed pioneering work in developing in-house automation and analysis tools. We achieve optimized PPA and lowest TTM with our homegrown design platform — Apollo. Apollo integrates intra-tool expertise and automates inter-tool communication for performance and consistency, delivering faster and predictable results.

Our solution is designed to produce the best performance for given power profile and area requirements — or alternatively, the lowest power and area for a given performance requirement. Apollo’s methodology is based on comprehensive and up-to-date understanding of design best practices as well as process nodes and their complexities. We have a thorough understanding of the reliability and tolerance ranges of the various process nodes offered by foundries along with processor, memory, IO requirements, and IP integration. The application of our team’s vast expertise gained over time is integrated into our modular platform, Apollo, which is easily customizable to each customer’s product. All of our services are enabled by our state-of-the-art data center, equipped with Apollo’s resource management and AI-acceleration software.

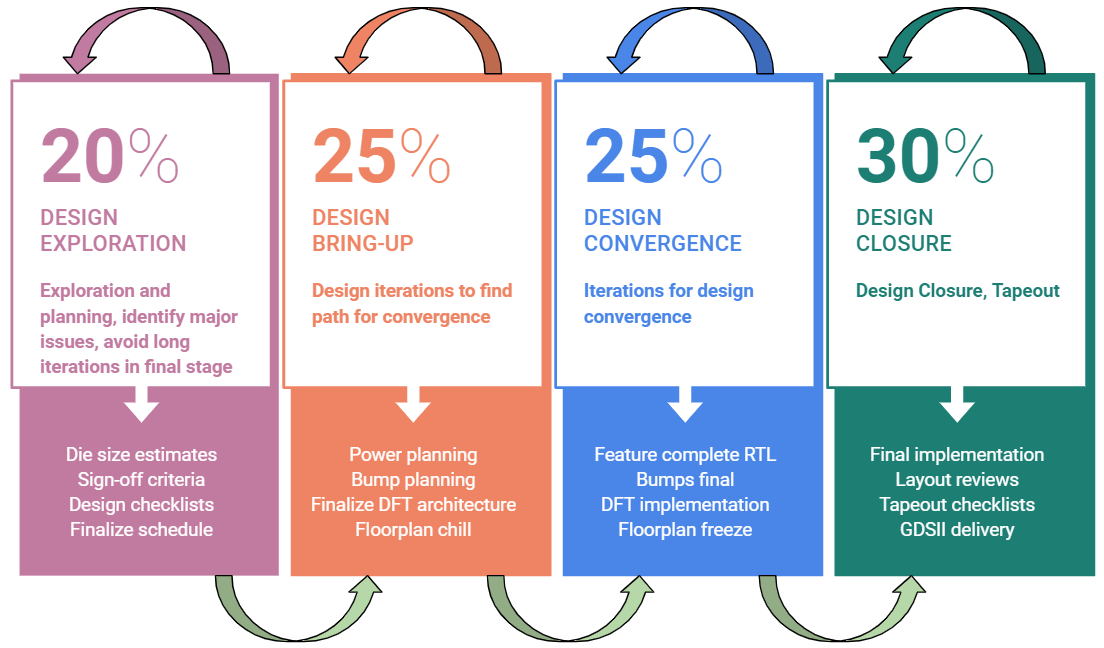

Phased Approach for Design Cycle

Our design execution is facilitated through four phases, each representing milestones that lead to on-time tapeouts. TTM is one of the most important metrics for any customer. Apex Semiconductor ensures lowest TTM with a predictive schedule. Each design phase is associated with a set of goals, dependencies, and outputs/metrics that are agreed upon with the customer before the project starts. The greatest benefits from reduced TTM are early feasibility studies and exploration. Apex provides customers with these “prep” packages to minimize the iteration time required to arrive at an optimized architecture and micro-architecture. Furthermore, each phase is iterative in nature and Apex provides constant feedback and collaboration with the customer. We also offer flexibility in terms of customizing design phases. Depending on project requirements, certain phases can be collapsed or extended if post-silicon activities are planned up-front with the customer. At the end of the first phase, Apex delivers the checklists that will be used for phase acceptance to the customer. The milestones for a given phase are considered complete only when the checklists are approved by all the parties involved.